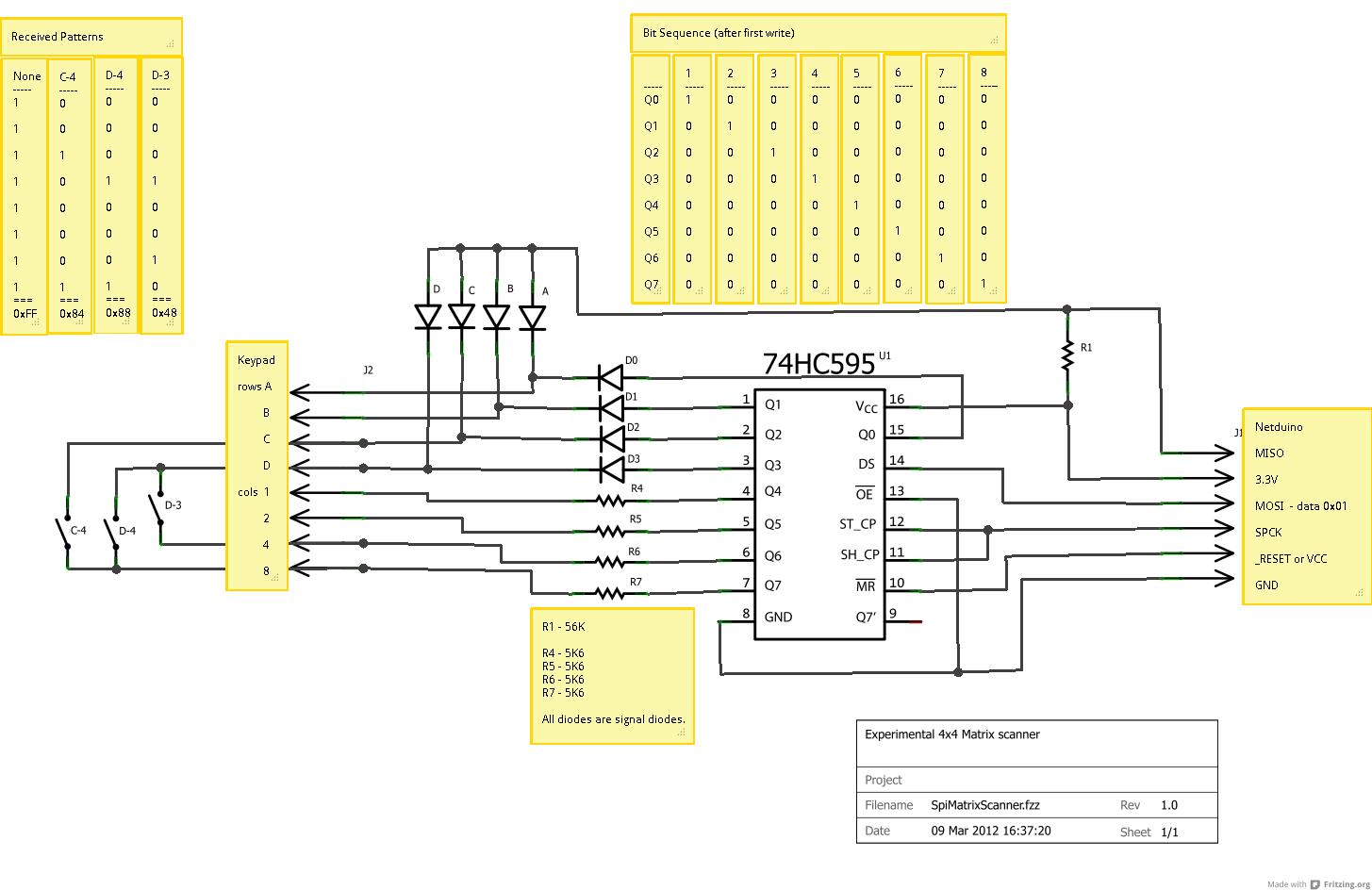

Of course, with this technique, you can daisy-chain as many ICs as you want. If you connect this pin to the SER pin of another 74HC595, and feed both ICs the same clock signal, they will behave as if they were a single IC with 16 outputs. This allows you to daisy-chain the 74HC595s. QH’ pin outputs bit 7 of the shift register.

QA–QH (Output Enable) are the output pins. When it is pulled LOW, the output pins function normally. OE (Output Enable) is also an active-low pin: when pulled HIGH, the output pins are disabled (set to high impedance state). Because this is an active-low pin, we must pull the SRCLR pin LOW to perform the reset. SRCLR (Shift Register Clear) pin allows us to reset the entire Shift Register, setting all the bits to zero.

So, the latch pin can be seen as the last step before we see our results at the output. When this pin is pulled HIGH, the contents of the Shift Register are copied into the Storage/Latch Register, which eventually appears at the output. RCLK (Register Clock / Latch) is a very important pin. This means that the bits are pushed in on the rising edge of the clock. SRCLK (Shift Register Clock) is the clock for the shift-register and is positive-edge triggered. SER (Serial Input) pin is used to send data into the shift register one bit at a time. VCC is the power supply for the 74HC595 shift register, which must be connected to 5V. The animation below will help you understand it better. As a result, whenever the value in the storage register changes, the output changes. Each bit of the storage register is linked to one of the IC’s output pins QA-QH. When the latch pin is enabled, the contents of the shift register are copied to the storage/latch register. This process will continue as long as 74HC595 is clocked. On the rising edge of the clock pulse, if the DATA pin is high, 1 is pushed into the shift register, otherwise 0.

0 Comments

Leave a Reply. |

RSS Feed

RSS Feed